Breaking: AMD's Mobile Chips Set to Revolutionize Performance with 3D V-Cache Technology

Technology

2025-02-18 19:58:59Content

AMD's upcoming Strix Halo processor is turning heads with its innovative die design, featuring Through-Silicon Via (TSV) technology that could potentially revolutionize future V-Cache implementations. The processor's architecture appears to be strategically engineered, with built-in TSV connections that pave the way for seamless integration of additional X3D V-Cache tiles in subsequent iterations.

These carefully positioned vertical interconnects suggest AMD is laying the groundwork for more flexible and scalable cache expansion. By incorporating TSV technology directly into the die, AMD creates a modular platform that could allow for easier cache tile additions without completely redesigning the entire processor architecture.

While details are still emerging, the reported design hints at AMD's forward-thinking approach to processor development. The Strix Halo's potential for future cache expansion could offer enthusiasts and professionals a tantalizing glimpse into the next generation of high-performance computing solutions.

Tech enthusiasts and industry watchers are eagerly anticipating more concrete information about this intriguing processor design, which seems to represent another innovative step in AMD's ongoing technological evolution.

Revolutionizing Computing: AMD's Strix Halo APU Breakthrough in Advanced Chip Design

In the rapidly evolving landscape of semiconductor technology, AMD stands poised to redefine computational capabilities with its groundbreaking Strix Halo architecture. This innovative approach represents a quantum leap in integrated processor design, promising to push the boundaries of performance, efficiency, and technological integration in ways that could fundamentally transform how we understand computing platforms.Unleashing Next-Generation Performance: The Future of Integrated Computing

Architectural Innovation: Decoding the X3D Cache Technology

The Strix Halo die represents a monumental engineering achievement that goes far beyond conventional processor design. Through the implementation of Through-Silicon Via (TSV) technologies, AMD has created a revolutionary pathway for future chip expansions. These microscopic vertical interconnects represent more than just a technical marvel; they symbolize a strategic approach to modular processor architecture that allows unprecedented flexibility in chip design. The TSV technology embedded within the Strix Halo die enables remarkable vertical integration, creating a three-dimensional approach to processor construction. By implementing these microscopic connections, AMD engineers have effectively created a scalable platform that can accommodate future cache expansions with minimal redesign requirements. This approach demonstrates a forward-thinking strategy that anticipates technological evolution rather than merely responding to current market demands.V-Cache Potential: A Glimpse into Future Computational Landscapes

The potential for V-Cache tile integration represents a paradigm shift in processor design philosophy. By creating a modular architecture that allows seamless cache expansion, AMD is essentially building a processor platform that can dynamically adapt to increasing computational demands. This approach challenges traditional processor development models, where chips are typically designed as static, immutable entities. The strategic placement of X3D Cache TSVs suggests a profound understanding of future computational requirements. By providing a flexible infrastructure that can accommodate additional cache tiles, AMD is positioning itself at the forefront of processor innovation. This methodology allows for potential performance enhancements without requiring complete chip redesigns, offering a cost-effective and technologically agile solution to the ever-increasing computational complexity of modern computing environments.Engineering Precision: The Technical Mechanics of Strix Halo

Delving into the intricate mechanics of the Strix Halo architecture reveals a masterclass in semiconductor engineering. The integration of Through-Silicon Via technologies represents a complex interplay of materials science, electrical engineering, and computational design. These microscopic vertical connections not only facilitate data transfer but also create a three-dimensional computational ecosystem that challenges traditional two-dimensional chip architectures. The precision required to implement these TSVs is extraordinary, involving nanoscale manufacturing processes that push the boundaries of current technological capabilities. Each via represents a potential pathway for enhanced data transfer, reduced latency, and improved overall system performance. By creating these vertical interconnects, AMD has effectively transformed the processor from a flat computational device into a dynamic, multi-layered computational platform.Market Implications and Technological Trajectory

The introduction of the Strix Halo architecture signals more than just a technological advancement; it represents a strategic repositioning within the competitive semiconductor landscape. By demonstrating the ability to create modular, adaptable processor designs, AMD is challenging established industry paradigms and setting new standards for computational innovation. This approach suggests a future where processors are not static products but dynamic platforms capable of continuous evolution. The implications extend beyond mere technical specifications, potentially reshaping how manufacturers, developers, and consumers conceptualize computing technology. The Strix Halo die becomes less a product and more a promise of future computational potential.RELATED NEWS

Technology

Breaking: Apple's M4 MacBook Air Crushes M1 in 7 Jaw-Dropping Upgrades

2025-03-08 10:30:00

Technology

End of an Era: Skype Bids Farewell After Decades of Digital Communication

2025-02-28 18:09:00

Technology

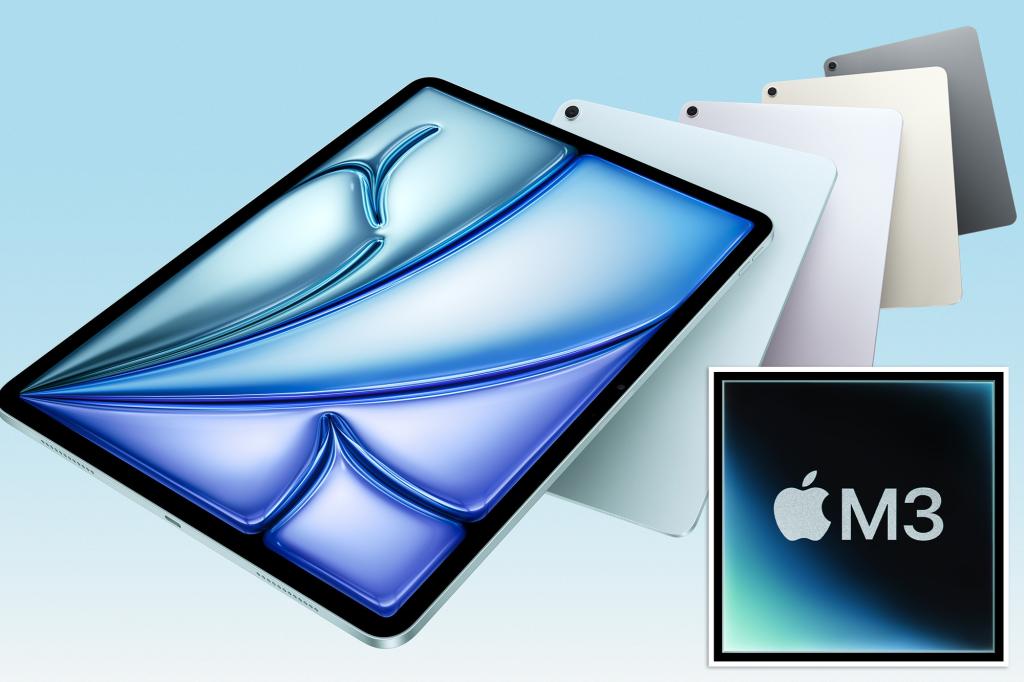

Sleek and Powerful: Apple's New iPad Air Signals MacBook Refresh on the Horizon

2025-03-04 20:33:14